Embedded Package Substrate Manufacturer.Embedded wafer-level-packages fan-out wlp chip embedded in substrate.High speed and high frequency material packaging substrate manufacturing. Advanced packaging substrate production process and technology.

The Evolving Landscape of Semiconductor Packaging

The world of semiconductors is continually advancing, with packaging playing a pivotal role in shaping the capabilities of electronic devices. As technology enthusiasts and engineers delve into the intricacies of semiconductor design, the packaging process emerges as a critical factor influencing overall performance.

Significance of Packaging Excellence in Chip Performance

In the relentless pursuit of enhanced chip performance, packaging stands as the unsung hero. The quality of packaging not only safeguards the delicate semiconductor components but also plays a decisive role in determining the efficiency, speed, and reliability of electronic devices. It acts as the silent force that propels technology forward.

Leveraging the power of Embedded Wafer-Level Packages (eWLP) has become a beacon of innovation, promising not just protection, but a paradigm shift in how we perceive and utilize semiconductor packaging.

Unveiling the Future: Embedded Wafer-Level Packages (eWLP)

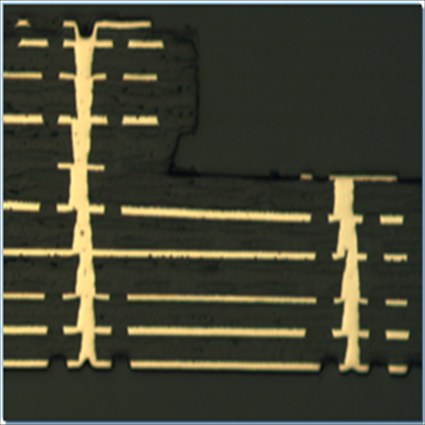

Enter the era of Embedded Wafer-Level Packages (eWLP), a revolutionary technology poised to redefine the boundaries of semiconductor packaging. This cutting-edge approach seamlessly integrates chips into the substrate, opening doors to a realm of possibilities in terms of compactness, performance, and versatility.

In the ever-evolving semiconductor landscape, where “smaller and faster” is the mantra, eWLP emerges as a game-changer, embodying the essence of miniaturization and efficiency. Fan-out technology within eWLP further amplifies its potential, promising not just compact designs but also optimized electrical performance.

As we embark on this exploration of eWLP, let’s unravel the layers of innovation that make it a cornerstone in the future of semiconductor packaging. From its fundamental concepts to real-world applications, we’ll journey through the transformative landscape of eWLP and its impact on the electronics industry.

Understanding Embedded Wafer-Level Packages (eWLP)

Definition and Key Characteristics of eWLP

Embedded Wafer-Level Packages (eWLP) represent a cutting-edge semiconductor packaging approach characterized by its compact design and integration capabilities. This innovative technology involves encapsulating the chip directly onto the wafer, eliminating the need for separate packaging components. Key characteristics include:

1.Miniaturization: eWLP leverages advanced manufacturing techniques to achieve a significantly smaller form factor, enhancing overall device compactness.

2.Cost Efficiency: By streamlining the packaging process and reducing material usage, eWLP presents a cost-effective solution for semiconductor manufacturers.

3.Enhanced Electrical Performance: The proximity of components within eWLP minimizes interconnect lengths, reducing signal delays and improving electrical performance.

Differentiating eWLP from Traditional Packaging Methods

Contrasting eWLP with traditional packaging methods underscores its transformative impact on the semiconductor industry. Key differentiators include:

1.Form Factor: Unlike traditional methods involving separate packaging components, eWLP integrates the chip directly onto the wafer, resulting in a more compact and space-efficient design.

2.Reduced Footprint: Traditional packaging often involves larger footprints due to the inclusion of multiple discrete components. eWLP’s integration approach allows for a more efficient use of space.

3.Thermal Management: eWLP’s design, coupled with fan-out technology, enhances thermal dissipation, addressing a longstanding challenge in traditional packaging methods.

The Role of Fan-Out Technology in eWLP

Fan-out technology serves as a cornerstone in the eWLP paradigm, providing crucial benefits for performance and reliability. Key aspects include:

1.Enhanced Signal Integrity: Fan-out technology redistributes I/Os, reducing the risk of signal interference and improving overall signal integrity.

2.Improved Heat Dissipation: The fan-out approach allows for a more efficient distribution of heat, preventing localized hotspots and enhancing the thermal management of the device.

3.Increased Integration Density: By facilitating the redistribution of components, fan-out technology enables higher integration density, supporting the integration of more functionalities within a smaller space.

As we delve deeper into the intricate workings of eWLP, it becomes evident that its integration with fan-out technology not only redefines the packaging landscape but also addresses critical challenges faced by traditional methods. This synergy sets the stage for a new era in semiconductor packaging, where efficiency, performance, and miniaturization converge to drive technological advancements.

Chip Integration in Substrate: A Game-Changer

Exploring the Concept of Chip Embedding in the Substrate

In the dynamic realm of semiconductor packaging, the concept of chip embedding within the substrate stands out as a revolutionary paradigm shift. This avant-garde approach involves seamlessly integrating chips directly into the substrate material, laying the foundation for what is known as Embedded Wafer-Level Packages (eWLP).

Key Concepts: Embedded Wafer-Level Packages (eWLP), Substrate Integration, Semiconductor Packaging

Advantages of Embedding Chips within the Substrate

1.Miniaturization and Form Factor Optimization:

eWLP leverages substrate embedding to reduce the overall footprint, enabling the creation of smaller and more compact electronic devices. This aligns with the industry’s pursuit of miniaturization without compromising performance.

2.Enhanced Electrical Performance:

Close proximity to the substrate enhances electrical connectivity, reducing signal delays and improving overall performance. This is particularly crucial in applications where high-speed data transfer and low latency are paramount.

3.Thermal Management Efficiency:

The integration into the substrate facilitates improved thermal dissipation, mitigating heat-related challenges often encountered in densely packed semiconductor devices. This ensures sustained performance and longevity.

4.Increased Reliability and Durability:

Embedding chips within the substrate enhances mechanical robustness, offering better resistance to external forces, vibrations, and thermal stress. This results in increased reliability, particularly in applications demanding ruggedness.

Comparisons with Conventional Packaging Approaches

1.Size and Weight Considerations:

eWLP’s substrate integration contrasts sharply with traditional packaging, where discrete packages add bulk. This makes eWLP ideal for applications demanding lightweight and compact designs.

2.Signal Integrity and Performance:

Compared to conventional packaging, eWLP excels in maintaining signal integrity, courtesy of reduced interconnect lengths. This is critical in applications like high-frequency communication and data processing.

3.Cost-Efficiency and Manufacturing Scalability:

The streamlined eWLP process simplifies manufacturing, potentially reducing costs compared to traditional methods. Additionally, the reduced number of components enhances scalability, making it an attractive choice for mass production.

4.Environmental Impact:

eWLP’s integrated design aligns with eco-friendly initiatives, as it reduces the need for additional materials and supports a more sustainable approach to semiconductor packaging.

Comparative Analysis: Size and Weight, Signal Integrity, Cost-Efficiency, Environmental Impact

In conclusion, the integration of chips within the substrate, as exemplified by eWLP, marks a transformative leap in semiconductor packaging. Its advantages in miniaturization, enhanced performance, and cost-effectiveness position it as a game-changer, challenging the conventions of traditional packaging approaches. This shift not only caters to the ever-evolving demands of modern electronics but also sets the stage for a more sustainable and efficient semiconductor industry.

Engineering Perspectives: Challenges and Solutions

Addressing Technical Challenges in Implementing eWLP

1.Miniaturization Dilemma:

Challenge: Achieving miniaturization without compromising performance.

Solution: Leveraging advanced fabrication techniques and materials to maintain or enhance chip performance in smaller form factors.

2.Thermal Management:

Challenge: Managing increased heat density due to the compact design of eWLP.

Solution: Integrating innovative thermal dissipation materials and optimizing fan-out structures for efficient heat dissipation.

3.Signal Integrity in Fan-Out:

Challenge: Ensuring robust signal integrity in fan-out configurations.

Solution: Employing advanced signal integrity analysis tools and materials, such as high-density interconnects, to maintain signal quality.

Solutions and Advancements in eWLP Technology

1.Advanced Materials Utilization:

Solution: Introducing novel materials with enhanced electrical properties for substrate and interconnect layers, ensuring improved overall performance.

2.Innovative Fan-Out Designs:

Solution: Developing optimized fan-out architectures to minimize signal interference, enhance electrical performance, and accommodate diverse chip layouts.

3.Integration of AI in Design:

Solution: Utilizing artificial intelligence algorithms to optimize chip placement, routing, and fan-out configurations, leading to more efficient and reliable eWLP designs.

Collaborative Efforts in the Engineering Community to Overcome Obstacles

1.Industry Standards and Knowledge Sharing:

Collaboration: Establishing industry-wide standards for eWLP technology to facilitate seamless integration and interoperability.

Knowledge Sharing: Encouraging open forums, conferences, and online platforms for engineers to share insights, best practices, and solutions.

2.Interdisciplinary Collaboration:

Collaboration: Promoting collaboration between semiconductor engineers, material scientists, and AI specialists to address multifaceted challenges.

Cross-Disciplinary Solutions: Fostering interdisciplinary research to create holistic solutions that consider both material and design aspects of eWLP.

3.Education and Training Programs:

Collaboration: Partnering with educational institutions and industry organizations to develop training programs focused on eWLP technology.

Skill Development: Empowering engineers with the necessary skills and knowledge through workshops and training sessions to effectively implement and troubleshoot eWLP solutions.

By actively addressing these technical challenges, implementing innovative solutions, and fostering collaborative efforts within the engineering community, the semiconductor industry can propel the adoption of Embedded Wafer-Level Packages (eWLP) into a new era of efficiency, performance, and reliability.

Applications and Industries Impacted

Overview of industries benefiting from eWLP technology

1.Telecommunications and 5G Infrastructure

Leveraging eWLP for compact, high-performance chips in base stations.

Enhancing signal processing efficiency in 5G networks.

2.Consumer Electronics

Integration of eWLP in smartphones for space-efficient and powerful processors.

Improving energy efficiency in wearables and smart devices.

3.Automotive Sector

Implementation of eWLP in advanced driver-assistance systems (ADAS).

Compact and robust chip packaging for in-vehicle entertainment systems.

4.Medical Devices

Utilizing eWLP for miniaturized and high-performance medical sensors.

Enhancing the reliability of implantable medical devices.

Real-world applications and success stories

1.Smartphones and Wearables

Case study: Leading smartphone manufacturer adopting eWLP for flagship models.

Success story: Wearable device with eWLP, achieving a breakthrough in size and functionality.

2.Automotive Innovations

Real-world application: eWLP-enabled sensors enhancing safety features in automobiles.

Success case: Integration of eWLP in electric vehicle control units for optimal space utilization.

3.Telecommunication Infrastructure

Implementation in 5G base stations: Case study on a network provider optimizing performance with eWLP.

Success story: eWLP-enabled components reducing latency in communication networks.

Potential for innovation in various sectors

1.Internet of Things (IoT)

Exploring the potential of eWLP in creating compact, efficient IoT devices.

Enabling seamless connectivity in smart homes and industrial IoT applications.

2.Artificial Intelligence (AI) Accelerators

Innovations in chip design using eWLP to support AI processing capabilities.

Reducing the footprint of AI hardware in edge computing applications.

3.Space Technology

Potential applications of eWLP in satellite systems and space exploration.

Addressing the challenges of size and weight constraints in spaceborne electronics.

Incorporating Embedded Wafer-Level Packages (eWLP) into various industries has not only enhanced the performance of existing applications but has also paved the way for groundbreaking innovations. From the seamless integration of eWLP in smartphones to its pivotal role in advancing 5G infrastructure, the technology’s versatility is driving transformative changes across sectors. As we delve into real-world success stories, it becomes evident that eWLP is not just a technological advancement; it’s a catalyst for pushing the boundaries of what’s possible in the realm of semiconductor packaging. The ongoing and potential applications of eWLP showcase its pivotal role in shaping the future of diverse industries, resonating with the ever-evolving needs of the technological landscape.

Flip-Chip Package Substrate manufacturer

Flip-Chip Package Substrate manufacturer